QSFP-DD光トランシーバーの給電方法:電源設計(3/3 ページ)

単相〜4相、1〜4出力、最大20A、設定可能バックコンバーター

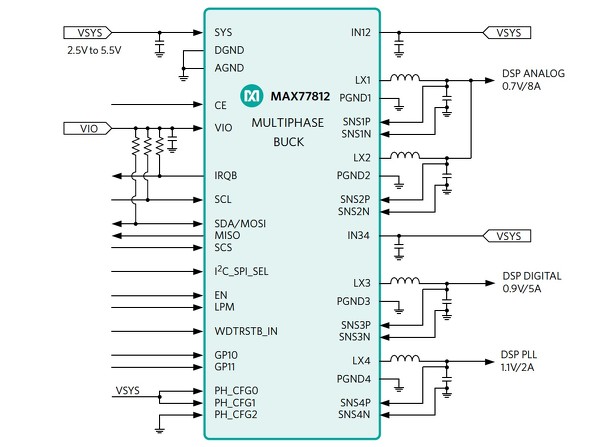

一例として、設定可能、単相〜4相、1〜4出力高電流、バック(ステップダウン)コンバーターを図9に示します。このデバイスは効率が高く、実装面積も小さく済む上、高い出力電圧精度、高速過渡応答、高速シリアルインタフェースオプションを備えているため、光トランシーバープリケーションのDSP/PHYの給電に適しています。柔軟なアーキテクチャによって、“4”(1つの4相出力)、“3+1”(2出力、1つの3相と1つの単相)、“2+2”(2つの2相出力)、“2+1+1”(3出力、1つの2相、2つの単相)、“1+1+1+1”(4つの単相出力)などの位相構成が可能です。

シングルチップによるシステム電力の処理

適切な構成を選択することによって、1つのICで図3の光トランシーバーのDSP/PHYに給電することができます。図9では、“2+1+1”構成でDSP/PHYデジタル、アナログ、PLLセクションに給電可能です。

効率

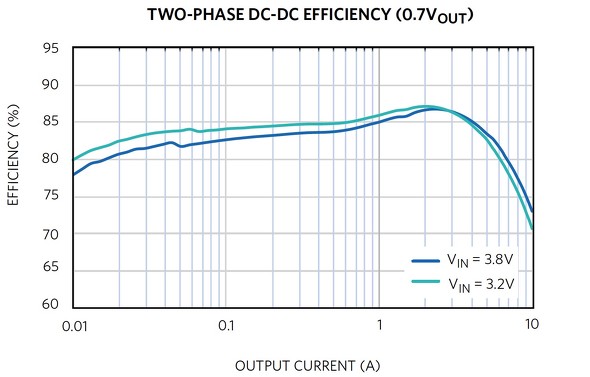

このデバイスの2相の効率曲線を、最大10Aまでの電流の範囲で図10に示します(0.22μH、2520サイズのインダクター)。

2相アーキテクチャによって、非常に低いデューティサイクル(低いVOUT)でも高効率が実現されます。

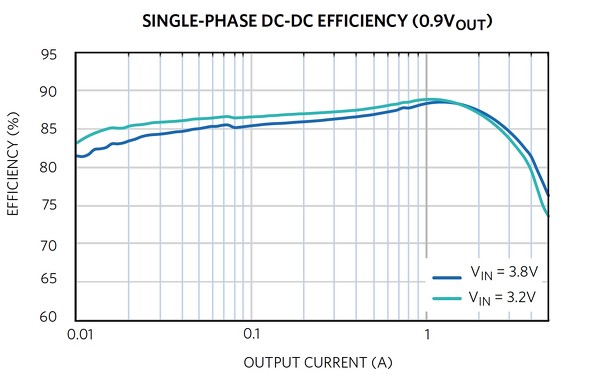

このデバイスの単相の効率曲線を、最大5Aまでの電流の範囲で図11に示します(0.22μH、2520サイズのインダクター)。

高効率、超小型シングルバックコンバーター

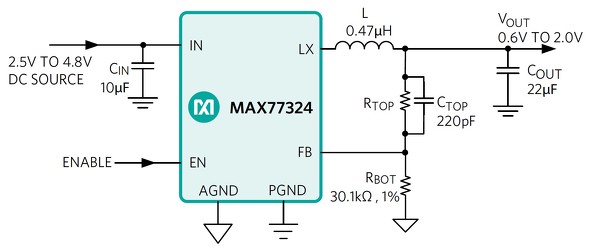

図4の単相バックコンバーターは、図12に示すアプリケーション回路で実装することができます。

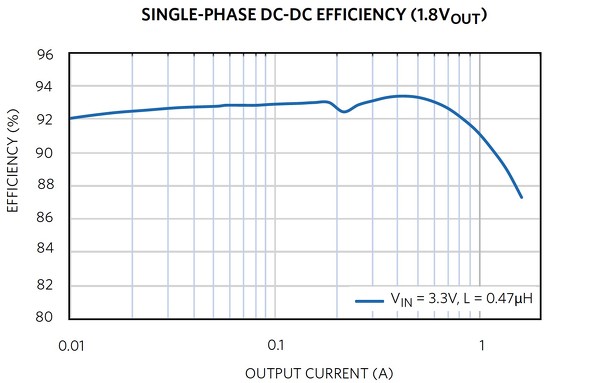

1.8V出力での効率曲線を図13に示します。このソリューションは、動作範囲の大部分にわたって+90%という優れた効率を提供します。

このアプリケーション回路が占有するスペースは、約7mm2です。

まとめ

QSFP-DDデバイスの各クラスで許容される最大消費電力の制約内で高データレートを提供するという光トランシーバーの課題について解説しました。単相〜4相、1〜4出力の高電流バックレギュレーターは、高効率および、小型PCBサイズを備えているため、高データレート光トランシーバーへの給電に適しています。

関連記事

低コストの100Gビット/秒光トランシーバー製品群

低コストの100Gビット/秒光トランシーバー製品群

ウェーブスプリッタ・ジャパンは、インターネットや携帯網のブロードバンド化に対応する5種類の100Gビット/秒(Gbps)光トランシーバー製品「WST-QS28」シリーズを発表した。従来のIEEE LR4準拠製品に比べ、3〜5割程度コストを低減できる。 SFPモジュール対応の光インタフェースコネクター

SFPモジュール対応の光インタフェースコネクター

日本航空電子工業は、屋外向けの光インタフェースコネクター「FO-BD6」シリーズを発売した。3軸フローティング機構を採用し、SFP対応モジュールを1つの動作で光ネットワークに接続できる。 100Gbpsの高速伝送に対応、QSFP28アクティブ・オプティカル・ケーブル

100Gbpsの高速伝送に対応、QSFP28アクティブ・オプティカル・ケーブル

富士通コンポーネントは、100Gビット/秒と高速伝送に対応できるマルチモードQSFP28アクティブ・オプティカル・ケーブル(AOC)のサンプル出荷を始めた。「InfiniBand EDR」や「100Gigabit Ethernet」の伝送速度に準拠しており、伝送距離は最大100mまで可能である。サーバーラック間やサーバー間といった近距離高速伝送用途に向ける。 高電圧向けバックコンバーターとコントローラー

高電圧向けバックコンバーターとコントローラー

Maxim Integrated Productsは、小型の高電圧車載電源用バックコンバーター「MAX20004」「MAX20006」「MAX20008」と同期整流バックコントローラー「MAX20098」「MAX20034」を発表した。 DC-DCコンバーターの出力フィルタリング

DC-DCコンバーターの出力フィルタリング

今回は、DC-DCコンバーターの出力フィルタリングを解説します。 複数電源の立ち上がり特性を制御する回路

複数電源の立ち上がり特性を制御する回路

大規模LSIチップを駆動するためには、複数の電源電圧が必要になることがある。こうした複数の電源電圧をLSIに供給する際に、それぞれの電源電圧をどのように供給し始めればよいかはLSIごとに異なっている。このため、使用するLSIに適した電源供給順序を実現する回路が不可欠である。今回は、単一の入力電圧から2系統の電圧出力を生成する電源回路を紹介する。

Copyright © ITmedia, Inc. All Rights Reserved.