半導体(1) ―― 半導体の製造工程:中堅技術者に贈る電子部品“徹底”活用講座(60)(2/2 ページ)

» 2021年11月29日 11時00分 公開

[加藤博二(Sifoen),EDN Japan]

後工程

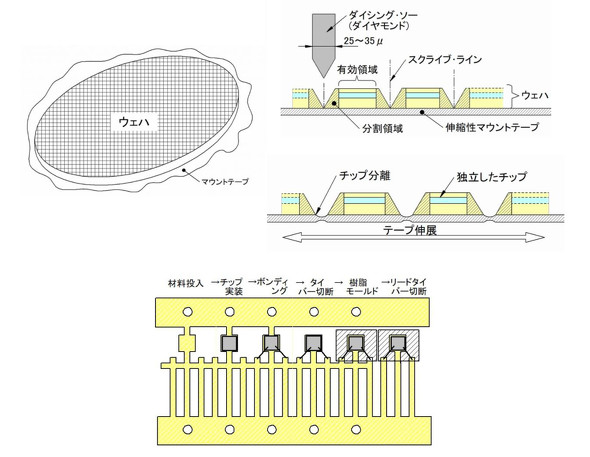

図4、表2にトランジスタを例に後工程を説明します。ICやダイオードの場合はリードフレームの形状が変わるだけで流れとしては同じです。またパワートランジスタなどは連続したフレームではなく、6〜20個取り用の短冊状のフレームを使います。

| ダイシング&エキスパンド | ウエハーを所定の分割線で切断し、個片のチップに切り分けます。ウェハーに入れる切削溝の深さによってフルカットとハーフカットの2つの手法があります。 |

|---|---|

| チップ実装 | チップを所定の位置にはんだ、あるいは銀ペーストなどで固定します。 |

| ボンディング | 外部電極との間を金線、アルミ線、銅線などで配線します。 |

| モールド&マーキング | エポキシ樹脂でモールドし、レーザーなどで品番、管理番号などを刻印します。 |

| メッキ | はんだ付けがしやすいように外部リードをはんだメッキ処理します。 |

| リードベンド/カット | 必要に応じてリードの曲げ加工を行います。 |

| (アバランシェ検査) | MOSFETのアバランシェ機能の検査を行います。破壊検査ですので全数波形管理が必要です。 |

| 耐圧試験 (一次側部品) |

一次側に使用するモールド品は必要な箇所を全数耐圧検査します。プローブが確実に接触していることの確認が重要です。 |

| 選別(検査) | 所定の電気特性を検査します。検査条件は3σ管理(IDSS、IGSS等二山分布品の検出)が求められます。 |

| テーピング | 所定の形状のテーピングを行います。 |

| 表2:後工程の概要 | |

前工程でチップ表面に保護膜を張るために20年ほど前までは後工程は通常の雰囲気中で行われていましたが品質向上活動が進むにつれて順次、防じんルーム→準クリーンルーム→クリーンルームと環境の向上が図られ、今では一部の製品を除いて組立工程は準クリーンルーム以上の環境で行われています。

次回は筆者が経験した半導体の不良について前工程、後工程、使い方などに分類して説明したいと思います。

執筆者プロフィール

加藤 博二(かとう ひろじ)

1951年生まれ。1972年に松下電器産業(現パナソニック)に入社し、電子部品の市場品質担当を経た後、電源装置の開発・設計業務を担当。1979年からSPICEを独力で習得し、後日その経験を生かして、SPICE、有限要素法、熱流体解析ツールなどの数値解析ツールを活用した電源装置の設計手法の開発・導入に従事した。現在は、CAEコンサルタントSifoenのプロジェクト代表として、NPO法人「CAE懇話会」の解析塾のSPICEコースを担当するとともに、Webサイト「Sifoen」において、在職中の経験を基に、電子部品の構造とその使用方法、SPICE用モデルのモデリング手法、電源装置の設計手法、熱設計入門、有限要素法のキーポイントなどを、“分かって設計する”シリーズとして公開している。

関連記事

共振子(1) ―― 水晶デバイスとは

共振子(1) ―― 水晶デバイスとは

今回からはマイコンや各種発振器、フィルターに使われる共振子について説明していきます。これらの共振子は回路的には完成度が高く、指定された使い方を間違えなければ正しく動作します。発振器として市販されている部品もありますので適材適所で使い分けることが肝心になります。 電気二重層キャパシター(4) ―― 主な特性と使用上の注意点、寿命計算

電気二重層キャパシター(4) ―― 主な特性と使用上の注意点、寿命計算

今回はEDLCにおいて重要視される特性や注意事項、寿命計算の考え方について説明をしたいと思います。 電気二重層キャパシター(1) ―― 概要と原理

電気二重層キャパシター(1) ―― 概要と原理

今回からはキャパシターの一種である電気二重層キャパシター(EDLC)について説明していきます。EDLCは、耐圧は低い(数ボルト以下)のですがその容量はファラド(F)単位になり、大容量と言われるアルミ電解コンデンサーの数百倍から数千倍のエネルギー密度になります。 セラミックキャパシター(6) ―― 新しい構造

セラミックキャパシター(6) ―― 新しい構造

過去2回にわたってセラミックキャパシターの温度特性について説明してきました。今回は最近のセラミックキャパシターに用いられる新しい構造について説明したいと思います。 セラミックキャパシター(5) ―― 高誘電率系キャパシターの温度特性

セラミックキャパシター(5) ―― 高誘電率系キャパシターの温度特性

高誘電率系のキャパシターの温度特性について説明します。この種のキャパシターの温度特性は数式で変化の様子を表すことができません。したがって図表や文章での説明が主体になります。 セラミックキャパシター(4) ―― 温度特性

セラミックキャパシター(4) ―― 温度特性

セラミックキャパシターの温度特性について説明をしていきます。なお、今回、取り上げる温度特性はIEC規格クラス1やその日本版であるJIS規格のクラス1です。

Copyright © ITmedia, Inc. All Rights Reserved.

Special ContentsPR

特別協賛PR

スポンサーからのお知らせPR

Special ContentPR

Pickup ContentsPR

Special SitePR

あなたにおすすめの記事PR