半導体(7) ―― MOSFETのゲート駆動回路の注意点(2):中堅技術者に贈る電子部品“徹底”活用講座(66)(3/3 ページ)

並列駆動時のノイズの回り込みによる異常振動

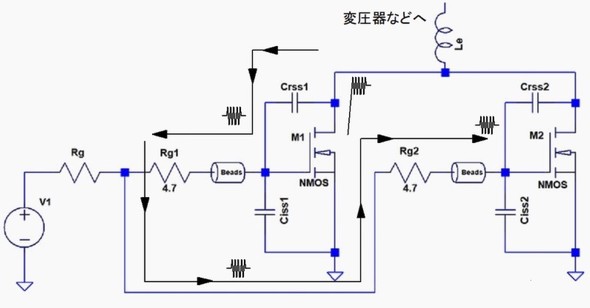

上記のようにシングルエンド形のスイッチング電源でもMOSFETの並列化によって大電力化に対応できることが分かります。しかし並列駆動方式では前述のアンバランス問題以外にもM1、M2間でノイズの回り込みがあり、回路の空間的、物理的バランスを取っても次のメカニズムで高周波振動が発生、成長する可能性があるので注意が必要です。

図7の例ではVth1>Vth2としています。

- ターンオフ時にM1が先に遮断されるとドレイン周辺の寄生Lや寄生CによってVdsに振動が発生します。

- M1のCrss1を通じてゲートに振動波形が誘起され、抵抗Rg1、2などを通じてM2のゲートに伝わり、まだ遮断されていないM2を高周波的にオンオフさせ、Vdsに振動を誘起します。

- この高周波振動はドレインを介してM1へ帰還されて振動をより一層悪化させ、M1、M2が破壊します。

このような動作を防ぐためにはゲートにバランス用を兼ねてRg1、Rg2を挿入するとともに該当する周波数域で信号を減衰させるフェライトビーズを挿入します。ただしフェライトビーズの高周波の損失が十分でないと逆にインダクタンス成分として作用して振動を逆に悪化させる場合があります。ゲート波形を観測しながら振動が誘起されないように材質を選択する必要があります。

ゲート異常振動の防止

本稿で説明した内容は基本セル単位で発生する可能性があります。つまり万単位で並んでいる基本セル間には各種の要因によって特性に微妙なバラツキが発生します。各種悪条件が重なってその中の1個のセルが異常振動して発熱すると隣接するセルへ熱が伝わる前に限界温度を超えて異常セルが熱破壊します。

この破壊品を開封して顕微鏡で観察すると別途説明するアバランシェ破壊の痕跡と類似の痕跡を見ることができます。しかしアバランシェ破壊かゲートの異常振動かを破壊痕だけから見分けるには周辺の動作波形とともに多くの経験が必要です。

前回も説明しましたが、このようなゲートの異常振動(発振)はそのままドレイン電流を断続します。過渡的な損失が周波数倍されて発生することはチップの焼損に直結するので絶対に発生を防止する必要があり、ゲート駆動波形にtf相当の段付きを設けるなど定数設定には余裕が必要になります。

このようなゲートの駆動波形は必要なら寄生容量の限度品を入手して調査することも視野に入れて負荷条件や入力条件を変えて確認してください。

次回はMOSFET特有の耐量であるアバランシェ耐量について説明します。

執筆者プロフィール

加藤 博二(かとう ひろじ)

1951年生まれ。1972年に松下電器産業(現パナソニック)に入社し、電子部品の市場品質担当を経た後、電源装置の開発・設計業務を担当。1979年からSPICEを独力で習得し、後日その経験を生かして、SPICE、有限要素法、熱流体解析ツールなどの数値解析ツールを活用した電源装置の設計手法の開発・導入に従事した。現在は、CAEコンサルタントSifoenのプロジェクト代表として、NPO法人「CAE懇話会」の解析塾のSPICEコースを担当するとともに、Webサイト「Sifoen」において、在職中の経験を基に、電子部品の構造とその使用方法、SPICE用モデルのモデリング手法、電源装置の設計手法、熱設計入門、有限要素法のキーポイントなどを、“分かって設計する”シリーズとして公開している。

関連記事

半導体(4) ―― 実際に経験した不良と対策(III)

半導体(4) ―― 実際に経験した不良と対策(III)

前回に引き続き、筆者が実際に半導体を使用する中で経験した思いがけない不良や原因が解明できていない不良について説明していく。 共振子(1) ―― 水晶デバイスとは

共振子(1) ―― 水晶デバイスとは

今回からはマイコンや各種発振器、フィルターに使われる共振子について説明していきます。これらの共振子は回路的には完成度が高く、指定された使い方を間違えなければ正しく動作します。発振器として市販されている部品もありますので適材適所で使い分けることが肝心になります。 電気二重層キャパシター(4) ―― 主な特性と使用上の注意点、寿命計算

電気二重層キャパシター(4) ―― 主な特性と使用上の注意点、寿命計算

今回はEDLCにおいて重要視される特性や注意事項、寿命計算の考え方について説明をしたいと思います。 電気二重層キャパシター(1) ―― 概要と原理

電気二重層キャパシター(1) ―― 概要と原理

今回からはキャパシターの一種である電気二重層キャパシター(EDLC)について説明していきます。EDLCは、耐圧は低い(数ボルト以下)のですがその容量はファラド(F)単位になり、大容量と言われるアルミ電解コンデンサーの数百倍から数千倍のエネルギー密度になります。 セラミックキャパシター(6) ―― 新しい構造

セラミックキャパシター(6) ―― 新しい構造

過去2回にわたってセラミックキャパシターの温度特性について説明してきました。今回は最近のセラミックキャパシターに用いられる新しい構造について説明したいと思います。 セラミックキャパシター(5) ―― 高誘電率系キャパシターの温度特性

セラミックキャパシター(5) ―― 高誘電率系キャパシターの温度特性

高誘電率系のキャパシターの温度特性について説明します。この種のキャパシターの温度特性は数式で変化の様子を表すことができません。したがって図表や文章での説明が主体になります。

Copyright © ITmedia, Inc. All Rights Reserved.