解析実行エラーの原因と対策(その3):SPICEの仕組みとその活用設計(8)(3/3 ページ)

SPICEモデルと過渡的電源の組み合わせでエラーになる例

上記のようにDC電源を緩やかに立ち上げれば全てOKになるわけではありません。そのような例としてMOSFETのSPICEモデルの特性解析時のエラー例を以下に示します。これらはSPICEモデルの等価回路と過渡的電流源の組み合わせが干渉した事例です。

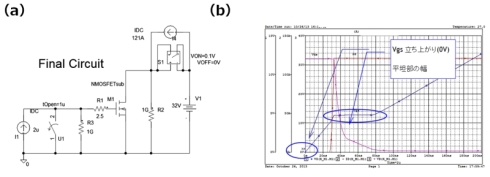

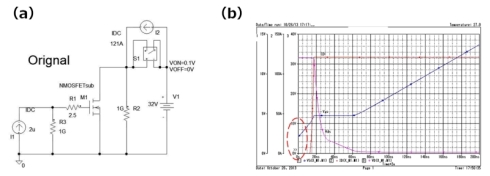

図4は、MOSFETメーカーの指定回路を再現したMOSFETのゲートチャージ特性を測定する回路です。

しかし、図4(b)の結果を見ると、Vgs曲線が本来は0Vからスタートしなければならないのに、破線の赤丸で示した部分のように0Vからスタートしていません。また、ICコマンドによる初期値を設定しても同じ結果です。

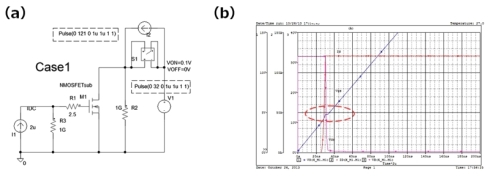

この対策として、MOSFET内部の寄生容量の充電電流がゲート電極から吐き出されて電圧が誘起されているものと考え、電圧源を1μSで立ち上げましたが改善が見られませんでした。そこで、図5(a)に示した対策1回路図のように、電流源も1μSで立ち上げてみました。

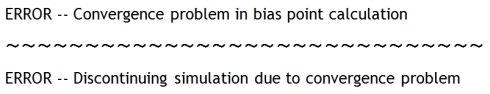

結果は、バイアスポイント計算で次のようなエラーを生じるとともに、図5(b)のようにVgs曲線の立ち上がり波形の平たん部が破線の赤丸で示した部分のように異常になっています。

原因

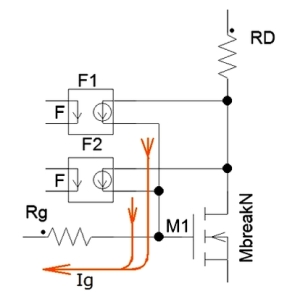

対象となったMOSFETはサブサーキットで構成されています。その問題部分を図6に示します。

このFデバイス(電流制御電流源)は、内部等価ダイオードの寄生容量の充放電電流を伝達するためのものですが、この電流がゲート電極周辺の寄生容量を過渡的に充電した結果、図4(b)のようにVgs電圧が0Vから立ち上がらなくなった原因になっています。さらに、これら2つのFデバイスの電流検出部は、ゲート〜ドレイン電圧に関連する素子の電流を検出していたため、図5(a)の対策1の回路ではループ状態になり各部の安定値を求めることができなかったのです。

対策

図5(b)のようになった原因は、過渡的電流源にすることにあるわけですから、図5(a)のような対策1回路は採用できません。図4(a)の原回路図を基に対策を考えます。

原因は図6のFデバイスの電流がゲート電極周辺の寄生容量を一時的に充電することにあるので、その期間中ゲート〜ソース間を短絡することを考えます。その結果を図7(a)と(b)に示します。これにより目的とした解析波形を得ることができました。

このことから、1つの対策に頼ることなく、原因を突き止めて適切な対策をとることが重要だということをご理解いただけたかと思います。

結局、回路動作を理解していないと正しい解析結果を得ることはできません。本連載で何回も述べているように、

「シミュレーション≠設計」

なのです。

注)今回の現象はゲート駆動回路を変更すれば解決しますが、メーカー指定回路の再現を優先した対策を紹介しました。スイッチング電源などの回路で使用するのであればこのような問題は発生しません。

次回はアナログ回路でしばしば用いられる正帰還回路とその初期値の問題、および解析手法の選択、そして解析問題のトラブルのまとめについて説明します。

執筆者プロフィール

加藤 博二(かとう ひろじ)

1951年生まれ。1972年に松下電器産業(現パナソニック)に入社し、電子部品の市場品質担当を経た後、電源装置の開発・設計業務を担当。1979年からSPICEを独力で習得し、後日その経験を生かして、SPICE、有限要素法、熱流体解析ツールなどの数値解析ツールを活用した電源装置の設計手法の開発・導入に従事した。現在は、CAEコンサルタントSifoenのプロジェクト代表として、NPO法人「CAE懇話会」の解析塾のSPICEコースを担当するとともに、Webサイト「Sifoen」において、在職中の経験を基に、電子部品の構造とその使用方法、SPICE用モデルのモデリング手法、電源装置の設計手法、熱設計入門、有限要素法のキーポイントなどを、“分かって設計する”シリーズとして公開している。

関連記事

- >>SPICEの仕組みとその活用設計

解析実行エラーの原因と対策(その2)

解析実行エラーの原因と対策(その2)

第6回では、SPICE解析を行う際に問題になる「収束エラー」のうち、「回路の特性」を原因とするものについて説明した。第7回では、「理想化の問題」と「解析設定条件」に起因する収束エラーとその対策について解説する。 解析実行エラーの原因と対策(その1)

解析実行エラーの原因と対策(その1)

SPICEの解析を実際に行う際に問題になるのが「解析実行エラー」だ。第6回では、解析実行エラーの原因の切り分けや、主因である「収束エラー」について説明する。

Copyright © ITmedia, Inc. All Rights Reserved.

図5(b)の解析におけるエラーメッセージ

図5(b)の解析におけるエラーメッセージ 図6 MOSFET内部等価回路

図6 MOSFET内部等価回路