Intelの14nmプロセス技術を用いた「Stratix 10」を発表、年内にテストチップ出荷:アルテラ Stratix 10/Arria 10(2/2 ページ)

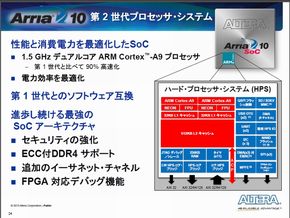

Arria 10は、1.5GHzのCortex-A9×2をサポート

Arria10の具体的な応用事例として、100Gワイヤライン通信用装置やデータセンター向け装置を挙げた。

Arria 10 SoCでは、動作周波数が1.5GHzのデュアルコアARM Cortex-A9プロセッサをサポートしている。プロセッサの動作周波数は現行品の800MHzに対して、今回は90%も高速化を図ったことになる。Arria 10のサンプル出荷は、2014年上旬を予定している。既に、早期アクセスプログラムに参加している顧客は、開発ソフトウェア「Quartus II」を用いて、Arria 10FPGAの設計を始めているという。さらに、FPGAベースのSoCを展開するに当たり、SoC製品でサポートしていくプロセッサのロードマップも紹介した。

Cyclone 10!? は、検討中

今回のGeneration 10の発表では、ローエンド製品の「Cycloneシリーズ」が含まれていなかった。これに対してDorsey氏は「ローコスト市場を狙ったシリーズも検討している」と話す。さらに2013年4月に発表したTSMCとの技術提携にも触れ、「TSMCと55nm Embedded Flash(EmbFlash)」プロセスを使った技術開発で提携した。この技術をGeneration 10で展開していく。どのファミリに応用するかはまだ明らかにできない。従来のエンベデッドフラッシュ技術を用いたFPGAに比べて、I/O当たりのコストを低減することができる」と述べるなど、55nm EmbFlash技術を用いた低コストファミリを用意する計画があることを明らかにした。

コンパイル時間を8倍高速に

Generation 10では、性能と電力効率を格段に改善した製品と同時に、開発環境も用意した。まず、ハードウェア設計者向けのQUARTUS IIは、コンパイル時間をこれまでより8倍も高速化できるという。また、QUARTUS IIとMATLAB/SimulinkツールをインタフェースするDSPシステム開発ツール「DSP Builder」の提供や、FPGA向けOpenCLのサポートなどがある。こうした生産性の高い開発環境を用いることで、ワイヤレス関連のコアとなる回路部分にFPGAベースのSoCを応用することが容易となった。

さらにDorsey氏は、Generation 10をベースとしたSoCを、ボードレベルで展開する場合の重要なコンポーネントとして電源モジュールを挙げた。Alteraは、ファブレスの電源ICメーカーであるEnpirionの買収を2013年5月に発表し、電源IC事業への参入を図った。Enpirion はFPGAやCPUといった先端IC用のDC-DCコンバータに特化した事業を展開してきた。Enpirion の電源モジュールは、外形寸法が競合製品を使ったものに比べて最大1/7のサイズにでき、高さも20%低く抑えることができるという。同社では、この電源ICを次世代FPGAで先行していくために必要なキーテクノロジの1つと位置付けている。

関連記事

アルテラが電源IC事業に参入、自社FPGAに最適な電源ICを開発/販売へ

アルテラが電源IC事業に参入、自社FPGAに最適な電源ICを開発/販売へ

アルテラは、電源ICメーカーのエンピリオンを買収する。アルテラは今後、自社FPGAに最適な電源ICを自社で開発し、FPGAとともに販売することになった。 シリコンコンバージェンスを可能とするアルテラSoC、開発環境も整う

シリコンコンバージェンスを可能とするアルテラSoC、開発環境も整う

FPGAベースの設計手法は、設計の柔軟性を確保しつつ最先端プロセス技術を活用できることから注目を集めている。こうした中で「シリコンコンバージェンス」を提唱しているアルテラは、最先端FPGA技術をベースとしたSoC設計を推進している。 アルテラが車載分野への本格展開を宣言、年率20%以上の売上高成長を見込む

アルテラが車載分野への本格展開を宣言、年率20%以上の売上高成長を見込む

FPGAベンダー大手のアルテラが、日本市場での車載展開を本格化させる。日本アルテラ社長の日隈寛和氏は、「車載分野専任の営業、技術サポート、マーケティングなどの人員がそろい、販売代理店としっかり連携できる体制がついに整った。これからは車載分野で積極的に展開を進めていく」と宣言した。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「通信エラー」の原因を追う――搬送機器のコントローラーを修理【前編】

- ARM台頭にルネサス誕生……時代に翻弄され続けた日立「SuperH」

- SDVとは? 定義や課題、時代に合わせたモビリティDX戦略の重要性

- フェライト(3) ―― 電子部品としてのフェライト

- アルミ電解コンデンサー(1)―― 原理と構造

- Ankerがイヤホン用AIチップ、NORフラッシュベースCiM処理

- オン抵抗30%低減 ロームの第5世代SiC MOSFET

- 独自の温度制御技術を搭載 TELの個片化デバイス向けプローバー

- 15G〜20GHz対応のウィルキンソン電力分配/合成器、Vishay

- 低速センサーレス制御技術搭載、三相BLDCモーター駆動IC