FPGAに向けた電源シーケンス回路:Design Ideas パワー関連と電源

システムを設計する場合、電源投入と電源切断のときに発生する、コア電圧(内部回路に供給する電源電圧)とI/O電圧(入出力回路に供給する電源電圧)のタイミングと、その電圧差に注意を払う必要がある。電源投入/切断時に3.3Vの入力電圧を1.8Vのコア電圧に変換し、I/O電圧は3.3Vを保つようにして、2つの電源電圧の差を最小に抑える回路を紹介する。

システムを設計する場合、電源投入と電源切断のときに発生する、コア電圧(内部回路に供給する電源電圧)とI/O電圧(入出力回路に供給する電源電圧)のタイミングと、その電圧差に注意を払う必要がある。

言い換えれば、電源シーケンスを考慮しなければならない。電源シーケンスが正しく実行されないと、ラッチアップや過電流の発生といった問題が起こる可能性がある。ラッチアップが起こる例としては、コアとI/Oに異なる値の電源電圧を入力した場合が考えられる。

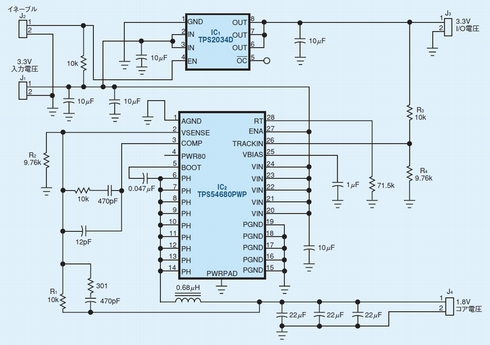

FPGAなどの電子部品では、コアとI/Oに対して、異なった電源シーケンス制御が必要となる。従って、電源システム設計が複雑になる。電源シーケンスに起因する問題を回避するには、電源投入時と電源切断時におけるコア電圧とI/O電圧との差を最小に抑えることが必要だ。図1は、電源投入/切断時に3.3Vの入力電圧を1.8Vのコア電圧に変換し、I/O電圧は3.3Vを保つようにして、2つの電源電圧の差を最小に抑える回路である。

この回路は、パワー・スイッチIC1「TPS2034」と降圧型スイッチング・レギュレーターIC2「TPS54680」で構成した。IC1はハイサイドのパワー・スイッチである。IC2がスタートアップ時に追従できるように、IC1はなだらかなランプ波形を描くように動作する。ランプ時間は6msで、パワー・スイッチと電源出力に接続したコンデンサーに流れる突入電流を最小にする。このように立ち上がりがゆっくりであるため、FPGAに流れ込む過渡電流を最小に抑えられる。

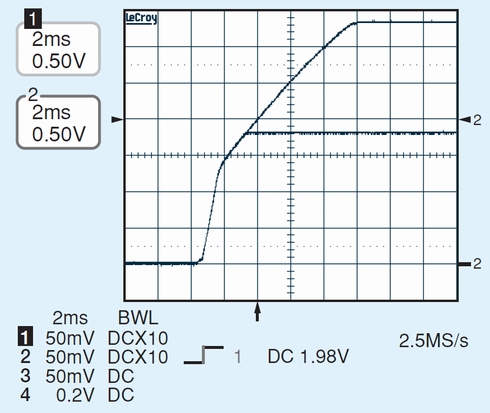

パワー・スイッチは、IC2がコア電圧を発生するために必要なバイアス電圧に達する前にI/O電圧を負荷に印加しないようにする役割を果たす。J1の入力電圧が3.3Vの場合、電源に接続されていないJ2コネクタはIC1をイネーブルにする。その後、I/O電圧J3は3.3Vに達するまでゆっくりと上昇して行く。I/O電圧が上がると、同時にコア電圧J4も1.8Vまで上昇する(図2)。

スイッチング・レギュレーターIC2には、電圧のトラッキング機能を実現するために、TRACKIN端子にアナログ多重化器を組み込んだ。電源投入/切断時にTRACKIN端子における電圧がIC内部の基準電圧である0.891V以下であれば、TRACKIN端子に入力した電圧は誤差増幅器の非反転端子に接続される。

0.891V以下であれば、この端子はスイッチング・レギュレーター回路の基準電圧として有効に機能する。TRACKIN端子に接続したR3とR4は分圧抵抗を構成する。電源投入/切断時に電圧差を最小にするためには、フィードバック補償用の分圧抵抗であるR1、R2と等しくする必要がある。IC1は、オン抵抗が37mΩのスイッチ素子を内蔵し、2A程度の電流を出力できる。IC2はオン抵抗が30mΩのMOSFETを2つ内蔵した同期整流方式の降圧型レギュレーターである。変換効率90%以上で、6Aの負荷電流を出力(ソース)、もしくは引き込む(シンク)ことができる。このため電源切断時でも別の電源電圧に出力を追従させることができる。

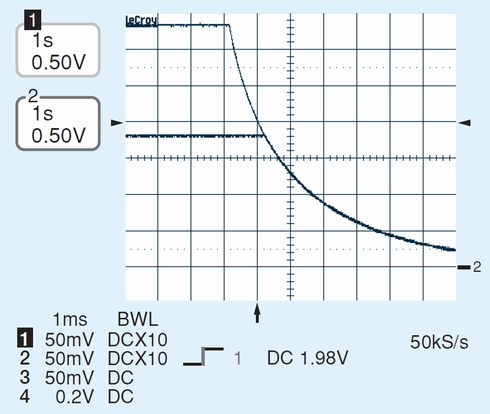

J2を接地してIC1をディスエーブルにすると、I/O電圧は下がり始め、さらにI/O電圧がコア電圧よりも低くなるとコア電圧もこれに追従して低下する(図3)。

通常、電源切断時にコア電圧とI/O電圧の差を固定するために、2つの電源回路の出力にショットキー・ダイオードを接続する。しかし図1の回路を使えば、ほとんどの場合、ショットキー・ダイオードは不要になる。さらに回路は、部品点数を削減できるというメリットもある。加えて、ラッチアップも発生せず、FPGAのスタートアップ時に発生する過渡電流も抑制できるため信頼性が向上する。

Design Ideas〜回路設計アイデア集

【アナログ機能回路】:フィルタ回路や発振回路、センサー回路など

【パワー関連と電源】:ノイズの低減手法、保護回路など

【ディスプレイとドライバ】:LEDの制御、活用法など

【計測とテスト】:簡易テスターの設計例、旧式の計測装置の有効な活用法など

【信号源とパルス処理】:その他のユニークな回路

※本記事は、2008年7月29日にEDN Japan臨時増刊として発刊した「珠玉の電気回路200選」に掲載されたものです。著者の所属や社名、部品の品番などは掲載当時の情報ですので、あらかじめご了承ください。

「珠玉の電気回路200選」:EDN Japanの回路アイデア寄稿コラム「Design Ideas」を1冊にまとめたもの。2001〜2008年に掲載された記事の中から200本を厳選し、5つのカテゴリに分けて収録した。

関連キーワード

電源 | 回路 | Design Ideas | FPGA関連 | FPGA | 設計 | レギュレータ | スタートアップ | コンデンサ | コネクタ(電子部品) | ダイオード | ディスプレイ | 電子部品(エレクトロニクス) | まとめ | MOSFET

関連記事

FPGAの進化を上回れ! 生産5年目に突如現れた起動不良

FPGAの進化を上回れ! 生産5年目に突如現れた起動不良

FPGAはハードウェアをプログラムできるデバイスで機器の高性能化や小型化には欠かせなくなってきている。複数のFPGAが実装される基板も多くなった。今回は、重要部品となったFPGAに起因したと思われるトラブルと、その原因について詳しく調査を行ったので紹介する。 スマートメーターの低消費電力設計

スマートメーターの低消費電力設計

世界規模で電力消費を削減し、電力使用量と請求情報を簡単に収集できると同時に、利用者が再生可能な電力買い取り制度の恩恵を享受するために、スマートメーターを本格展開することは重要な一歩です。ただし、スマートメーターの設計には標準が存在せず、設計が異なると電力供給方式も異なります。本稿は、スマートメーターの電源設計者が直面するいくつかの課題について考察し、ソリューションを紹介します。 プログラマブル・ロジックを使ったVCO

プログラマブル・ロジックを使ったVCO

可変周波数の発振器を構成する方法として、NORゲートを2個用いたRC発振回路を考案した。この回路による可変周波数範囲は広い。

Copyright © ITmedia, Inc. All Rights Reserved.

図2 電源投入時の電源電圧波形

図2 電源投入時の電源電圧波形 図3 電源切断時の電源電圧波形

図3 電源切断時の電源電圧波形