差動伝送路のケーブル・コネクターの選び方と設計上の注意:高速シリアル伝送技術講座(8)(5/5 ページ)

LVDS 低速使用時の高い汎用性と性能

ここまで、差動高速伝送は「差動信号用のインピーダンス整合が取れたコネクターとケーブルの使用が条件」と説明していきました。しかしLVDSの低速アプリケーションでは、LVDS物理層のエッジレートが高速でないため、シングルエンド汎用コネクターや安価な伝送媒体も、設計を工夫することで使用可能となります。ここではその選定と設計方法を説明していきます。

LVDSの低速(おおよそ200M〜300Mbps以下)で伝送距離が短い場合は、シングルエンド信号で使用される不平衡ケーブル(リボンケーブル/フレキシブルフラットケーブル、複数の銅線が束ねられた差動特性インピーダンスの定義がないケーブル)やそのコネクターも、ピンアサインを差動用に最適化することで流用が可能です。ただし受信端の波形がインピーダンス不整合の反射の影響で1ビット時間以内に安定しない場合は、終端抵抗値の調整や終端部にキャパシターやインダクターを追加し高周波成分の反射を吸収、減衰させる工夫が必要かもしれません。

LDVS 汎用リボンケーブル・フレキシブルフラットケーブル(FFC)の使用

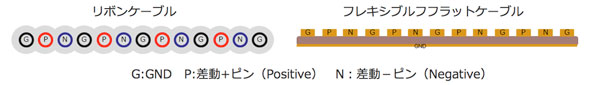

図18のようなリボンケーブルや汎用FFCは差動信号用ではない不平衡ケーブルですが、図19のような差動のピンアサインとすることで、安定した差動の特性インピーダンスが発生する構成となり、各種LVDSのアプリケーションで使用されています。

差動ペア間のクロストークの改善が必要な場合は差動ペア間のGNDを追加し、GPNGGPNGGPNGGPNGG……のピンアサインとします。他のシングルエンド信号が配線される場合も同様にGNDを追加し距離を離し電気的なアイソレーションを強めます。

あるリボンケーブル(1.27mmピッチ)の差動特性インピーダンスをTDRで測定した結果、特性インピーダンスは180Ω、FFC(0.5mmピッチ)では110Ωでした。よってこのリボンケーブルの使用では終端抵抗値を180Ω、FFCでは110Ωで終端し、終端抵抗値を伝送路の特性インピーダンスに整合させると、受信端での反射を防いで安定した信号伝送が可能となります(注:これら並行ケーブルは導体太さ、材質(誘電体)、導体間距離によりインピーダンスは大きく異なり、一定ではありません。またLVDS規格の終端抵抗の範囲は90〜132Ωです)。

FPC(フレキシブルプリンテッドサーキット)では、FFCのような固定の配線レイアウトではなく自由な配線設計が可能なため、前回記載したPCBの差動レイアウト方法と同様に、特性インピーダンス、インサーションロス、クロストークについても差動に特化した設計が可能です。

特性インピーダンスが定義されていない不平衡ケーブルでは、使用するケーブル長での特性インピーダンス(TDR)、インサーションロス、リターンロスを測定することで使用可能かを判断できます。

LVDS 汎用コネクターの選定と設計

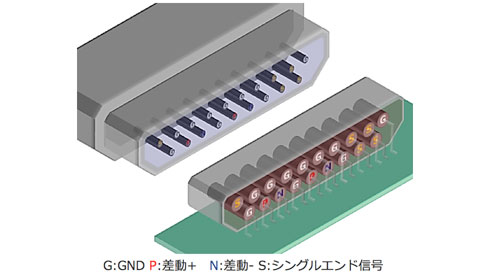

不平衡汎用コネクターをLVDSの差動伝送路に使用する場合、以下の点に注意し設計を行います。

- 差動結合が崩れないように差動ペアは隣り合ったピンをアサインにします。

- 差動ペア間はGNDピンを挟みアイソレーションします。

- シングルエンド信号がアサインされる場合はGNDピンでLVDS信号とアイソレーションします。

- コネクター内部の伝送長がなるべく短い製品を選びます。FFC/FPCコネクターは余分なインピーダンス不整合の伝送長が他のコネクターと比較し短く、ピン形状にスタブがなくシンプルなものは実力的に高帯域であることが特長です。

- コネクターのピン間ピッチの狭いものを使用します。差動間のピッチが狭いとインピーダンスの上昇による反射を少なくすることができます。

- プラグとレセプタクルのコネクターピン接合部で2段以上のピン配列ではインピーダンス不整合部分の長さを極力短くさせるため、基板に近い下側のピンを差動信号にアサインします。

- コネクターの端のピンはLVDS差動に割り当てません。差動ペアをGNDで挟み込むGPNGの配置になるようにアサインします。

図20は上記の条件をレセプタクル(基板側コネクター)のピンアサインの応用した例になります。

LVDSの低速では、コネクターとケーブルのインピーダンス特性が安定する構造になるようにピンアサインを行うことで、コネクター・ケーブルのコスト上昇を抑えながらシングルエンド信号をLVDSに変更し高速化が可能です。

低速差動通信のRS-422、RS-485やシングルエンド信号の高速化のためにLVDSへ変更するなどのアプリケーションではこの設計手法が有効です。

このようなピンアサインやピンピッチの考え方は高帯域のコネクターやケーブルの設計と基本的に同じです。そのため差動インピーダンスを配慮し設計されている低帯域向けアプリケーションのコネクターやケーブルは、潜在的に高帯域に対応できる可能性があり、インサーションロス、リターンロス、TDRの評価で実力を把握できます。

一例ですが、筺体内の基板間通信で一般的に使用されている、図14-2に示したFFC/PFC用コネクター(レセプタクル)では、ピンピッチにも依存しますがコネクターにアサインされるPN差動ペア内の特性インピーダンスをうまく作り込むことも可能で、コネクター(レセプタクル)内部のインピーダンス不整合となるピン部分も非常に短いため、一部を改良し10Gbpsを超える高帯域に使用できる場合があります。

またこのコネクターに使用されるFFC/FPCケーブルも伝送路が平行線のシンプルな構造のため、差動の結合を保持しながら配線が可能で、差動ペア内(Zodd)とシールドGND間(Zeven)のインピーダンス調整と低誘電正接の材質の使用で、指定の差動特性インピーダンスと高周波でのローロス設計が出できるようになってきています。

このようにコネクターメーカー、ケーブルメーカー、半導体メーカーが協力し、さまざまなアプリケーションで今後の高帯域化や低価格化に対応できる製品開発を行っています。

参考として10Gbpsを超える帯域のFFC/FPCケーブルとそのコネクター開発事例を以下に紹介します。ご興味のある方はご覧ください。

| ⇒ | 16Gbps(V-by-One US)フレキシブルフラットケーブルの開発(住友電気工業) |

|---|---|

| ⇒ | 16Gbps(V-by-One US)フレキシブルフラットケーブルの開発(東京特殊電線) |

| ⇒ | 16Gbps(V-by-One US)フレキシブルプリンテッドサーキットケーブルの開発(山一電機) |

| ⇒ | 16Gbps(V-by-One US)FFC/FPC向けコネクター出荷開始(ヒロセ電機) |

【参考文献】

・テクトロニクス 技術セミナーウィーク2016冬 高速信号設計の注意点 講演資料 河西基文

・ギガビット伝送システム開発力強化集中講座 CQエレクトロニクスセミナ2012 講演資料 河西基文.

・ナショナルセミコンダクタージャパン株式会社 LVDSオーナーズマニュアル 第3版/第4版

筆者Profile

河西基文(かわにし もとふみ)/ザインエレクトロニクス シニアエキスパート

ナショナルセミコンダクタージャパンやジェナムジャパンなど、25年にわたり高速通信系半導体の製品開発・サポートおよびマーケットの開拓に従事。伝送路を含んだ半導体の高速設計手法が確立されていない時代に、LVDSオーナーズマニュアルの作成など、同マーケットの成長・普及に寄与してきた。

現在は日本のSerDes製品開発の先駆者的存在のザインエレクトロニクスで、プロダクトマーケティング・開発支援や人材育成などを行っている。

関連記事

LVDS PHY製品と伝送路の設計(その1)

LVDS PHY製品と伝送路の設計(その1)

LVDS PHY(物理層)製品を使用する上で必要な一般的な知識とともに、伝送路の設計方法について詳しく解説していきます。 終端方式と高速シリアルI/Fデバイス

終端方式と高速シリアルI/Fデバイス

今回は、LVDS、CML/PECL、計測器などの終端方法と、シリアル伝送デバイスの種類について解説します。 接続形態(トポロジ)と特性インピーダンス

接続形態(トポロジ)と特性インピーダンス

今回は接続形態(トポロジ)、特性インピーダンスについてです。LVDS系テクノロジーのさまざまなトポロジとその基本な構成、またPECLやCMLを使用して同機能を高速で実現する方法などについて紹介します。 高速伝送の代表的な物理層 LVDS・PECL・CML

高速伝送の代表的な物理層 LVDS・PECL・CML

今回は、高速差動伝送で使用されている代表的な物理層である「LVDS」「PECL」「CML」の特長、接続方法、用途例を紹介していきます。 差動信号伝送のメリット ――使用されている技術と注意点

差動信号伝送のメリット ――使用されている技術と注意点

高速シリアル伝送技術について基礎から学ぶ本連載。2回目は、差動信号伝送の特徴、メリットに焦点を当て、使用されている技術や注意点について解説していきます。 PCIe、USB、Ethernet、HDMI、LVDSなど高速伝送技術の基本を理解するために

PCIe、USB、Ethernet、HDMI、LVDSなど高速伝送技術の基本を理解するために

本連載では、さまざまな高速通信規格に使用されている物理層の仕組みや性能、SerDesの機能や特徴とその種類、高速伝送での主要なパラメーター、伝送路を含んだ技術や設計手法などを分かりやすく解説していく。

Copyright © ITmedia, Inc. All Rights Reserved.

図18:リボンケーブル(左)とフレキシブルフフラットケーブル(FFC)

図18:リボンケーブル(左)とフレキシブルフフラットケーブル(FFC) 図19:フラットケーブルの差動ピンアサイン

図19:フラットケーブルの差動ピンアサイン 図20:差動信号に合わせたコネクターのピンアサインとその構造

図20:差動信号に合わせたコネクターのピンアサインとその構造