オペアンプICのPSRR特性を補強! 電源ノイズ耐性を高めるフィルタ回路:オペアンプ+トランジスタ“ちょい足し”回路集(8)

オペアンプICに個別トランジスタを“ちょい足し”して性能を高めたり機能を拡充したりできる定番回路集。今回は、トランジスタと抵抗、コンデンサを追加して、電源ノイズの抑圧性能を高め、出力に表れる電源変動の影響を抑える方法を紹介します。

今回紹介する回路の概要

| 実現できる機能 | オペアンプに供給する電源のノイズ成分を低減する。特に高周波のノイズ成分に効く。 |

|---|---|

| こんな場面で有効 | オペアンプと電源との間が離れている場合や、デジタル回路が混載されている基板などで、オペアンプに供給する電源にノイズが乗りやすい場合に使える。ただし、大電流がオペアンプ回路に流れる場合は、このフィルタ回路によって電源の電圧降下が生じるので、注意が必要である。 |

今回紹介する回路は、ローパスフィルタの一種です。オペアンプICの電源ラインに挿入すれば、電源系のノイズがオペアンプに与える悪影響を低減することが可能です。

一般に、オペアンプICにはPSRR(電源電圧変動除去比)という仕様が規定されています。これはオペアンプに供給されている電源電圧が変動したときに、オペアンプの出力がどの程度影響を受けるかという指標です。PSRRの値が高いほどノイズの影響が出力に表れにくく、電源電圧の変動に対して安定した性能が得られます。なお、PSRRを出力電圧で表すとオペアンプ回路の利得によって値が変化してしまうため、実際のオペアンプICのデータシートでは入力電圧に換算した値が記載されています。

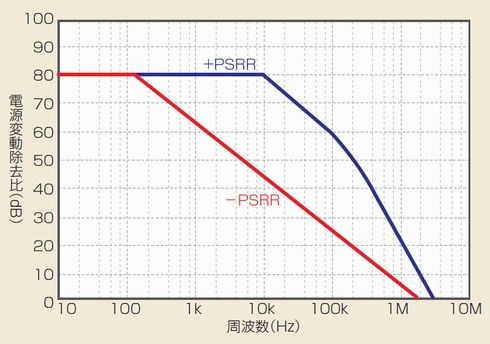

図1をご覧ください。PSRRにはこの例のように周波数特性があり、オペアンプICに供給される電源に重畳したノイズの周波数が高くなるにつれて除去性能が低下し、ノイズの影響が出やすくなる傾向があります(PSRR特性はこの他、温度でも変化します)。

オペアンプの電源ラインにローパスフィルタを挿入することで、PSRRの高周波数領域における特性の劣化を補償し、全体的な周波数特性を見かけ上改善しようというのが、今回の“ちょい足し”の目的です。

図1 PSRRの周波数特性 アナログ・デバイセズの高精度・低消費電力オペアンプIC「AD822」のPSRR(電源電圧変動除去比)を例として示しました。周波数が高くなるとPSRRは低下します。また、この図からは、電源の正負でPSRRの特性が異なることも読み取れます。

図1 PSRRの周波数特性 アナログ・デバイセズの高精度・低消費電力オペアンプIC「AD822」のPSRR(電源電圧変動除去比)を例として示しました。周波数が高くなるとPSRRは低下します。また、この図からは、電源の正負でPSRRの特性が異なることも読み取れます。オペアンプのPSRRについては、図1の例からも読み取れるように、電源の正負で特性が異なる点にも注意が必要です(これもオペアンプを使う際に配慮すべきポイントですので、ぜひ覚えておいてください!)。今回は簡単にするために、正側の電源のみを考えることにしましょう。

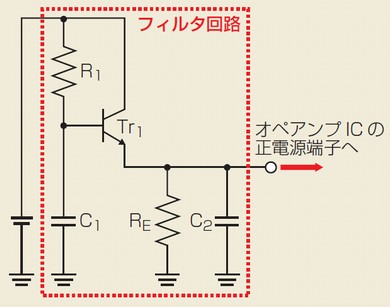

図2が今回のちょい足し回路です。トランジスタのコレクタ接地(エミッタ・フォロワ)回路構成となっています。抵抗R1とコンデンサC1を介してトランジスタTr1を駆動する形になり、ローパスフィルタを実現しています。

部品の選び方とシミュレーション結果

ローパスフィルタとしてのカットオフ周波数は、R1とC1の値で調整できます。

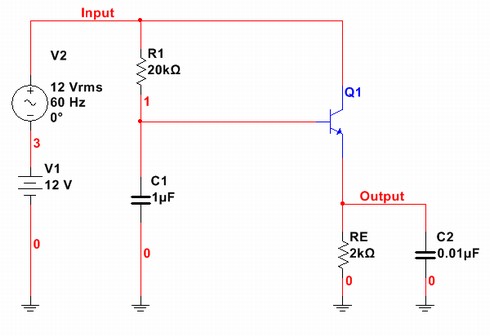

それではシミュレータで、このちょい足し回路の特性を確かめてみましょう。図3が回路図です。今回のシミュレーションでは、R1に20kΩ、C1に1μFを選びました。トランジスタは、シミュレータの標準ライブラリに用意されていた「2N2222」という少々古い品種で、素子パラメータはコレクタ容量(Cob)が8pF、直流電流増幅率(hFE)がIC=10mA時に75です。

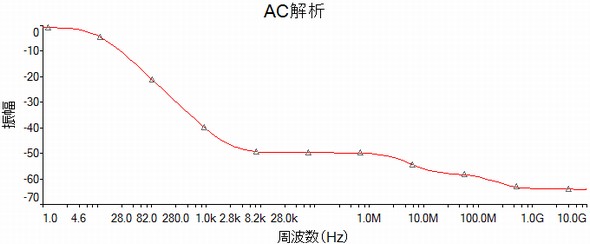

この回路のシミュレーション結果を図4に示します。

このように、今回のちょい足し回路を用いることで、ローパスフィルタの効果が出ていることが確認できました。これにより、周波数が高い領域でノイズ抑圧性能が低下するという、オペアンプICのPSRR特性を見かけ上改善することができます。

トランジスタからの供給電圧変動に対する考慮

トランジスタのエミッタには、内部抵抗reが存在しています。このreは、以下の式で表されるように、コレクタ電流ICに依存しています。

re = 26Ω/IC (mA) (26Ωは、1mA時のエミッタ側の動作抵抗値)

このため、オペアンプの電流消費量のダイナミックな増減によって、ICが変化することでreが変動し、結果としてオペアンプの電源電圧の電圧降下量に変動が起きてしまいます。この変動の影響を抑えて目立たなくさせるには、トランジスタのエミッタ出力と並列に抵抗とコンデンサ(図2の回路ではREとC2が該当)を追加する方法が有効です。

- 外付けFETの“電子抵抗素子”でゲイン制御アンプを実現、AGCにも応用可能

- 差動トランジスタを組み合わせて低ノイズアンプを作る

- 入力振幅に応じてゲインを調整する回路、ダイオード2個でソフトクランプを実現可能

- 電流信号をコピーする! カレントミラー回路をマスターしよう

- オペアンプICのPSRR特性を補強! 電源ノイズ耐性を高めるフィルタ回路

- 有事にアンプを守り、平時は何もしないダイオード回路

- 過電流や短絡電流の対策に使える電流クランプ回路

- 電圧制御のプログラマブル定電流源、デジタルコントロ−ルも容易

- 電源電圧や温度に依存しない高安定の基準電圧源を作る

- 思わぬ過電圧にも備えて安心、ダイオード利用の保護回路

- 駆動能力が足りない! 出力電流を手軽に稼ぐ法

- センサー励起や回路バイアスに使える定電流源

Copyright © ITmedia, Inc. All Rights Reserved.

図2 トランジスタを使ったリップルフィルタ このフィルタの出力をオペアンプICの正電源に供給します。

図2 トランジスタを使ったリップルフィルタ このフィルタの出力をオペアンプICの正電源に供給します。 図3 シミュレーションに用いた回路図

図3 シミュレーションに用いた回路図 図4 フィルタ回路の出力における周波数特性 横軸は周波数で単位はHz、縦軸は入出力間の振幅の比で単位はdBです。

図4 フィルタ回路の出力における周波数特性 横軸は周波数で単位はHz、縦軸は入出力間の振幅の比で単位はdBです。