SPICE応用設計(その2):フーリエ解析:SPICEの仕組みとその活用設計(13)(3/3 ページ)

損失の解析

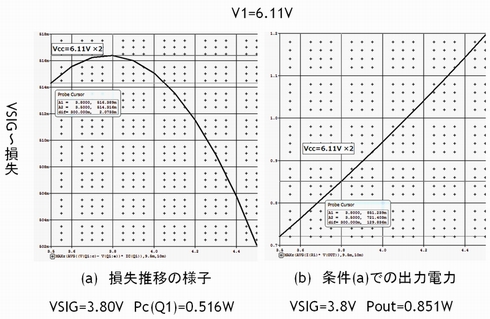

電源電圧V1は前回の検討によって最高6.11Vまで上昇すると分かっています。しかし、B級アンプの場合、最大出力時にトランジスタの損失が最大になるとは限りません。理論解は分かっているのですが、今回は確認のためにSPICEのパラメトリック解析機能を使って最大損失ポイントを求めてみます。バイアス回路は今回の検討で決めた図5の(3.3Ω+Diode)の回路を用います。

まず、入力信号V2のピーク値{VSIG}を変化させ、V1=6.11V時のQ1の損失をパラメトリック解析で求めます。

SPICEの解析結果を図9に示しますが、最大損失が発生する信号電圧は約3.80Vp時であり、その条件での解析結果としては、

- 出力電力……Po=0.851W

- 損失*3)……Pc(Q1)+Pc(Q4)=1.032W

- 効率 ……η=45.2%

を得ることができました。

*3)コレクタ損失Pcは瞬時電力(=Vce×Ic)の時間平均値を計算することで得ることができます。

コレクタ電流Icがキッチリとした半波正弦波でなく、両端で鈍っている影響で少し低めの信号電圧で損失最大点を迎えており、効率も50%を下回っていますが、実力的には市販のものと大差ありません。

ヒートシンクの放熱抵抗

上記の検討から、このオーディオアンプの放熱条件としてセット周囲温度30℃、機器内温度上昇20℃を考慮すると、ヒートシンクは周囲温度(Ta)が50℃の環境で1.03Wを放熱しなければなりません。

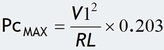

また、この時の半導体のジャンクション温度は150℃×0.8=120℃以下に抑えたいところです。したがって、放熱経路全体の熱抵抗Rthとしては、

Rth=(120−50)/1.03=68(K/W)

が要求されます。

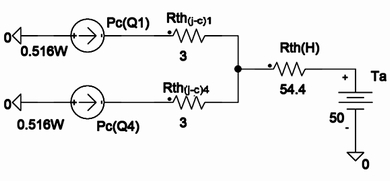

これらを考慮した熱的等価回路を図10に示します。

Q1,Q4のパッケージ裏面〜チップの熱抵抗Rth(j−c)を3(K/W)と見込めば、ヒートシンクの熱抵抗Rth(H)は、

Rth(H)=Rth−Rth(j−c)=68−3/2=66.5(K/W)

以下であれば良いことになります。

連載11回目のサブサーキットの例として紹介した熱抵抗解析モジュールの項で取り上げた、ヒートシンク、(H)20×(W)30×(T)2の熱抵抗Rth(H)は54.4(K/W)(Ta=50℃、P=1W時)ですので、このヒートシンクを使用した場合、Q1のジャンクション温度Tj(Q1)は、

Tj(Q1)=Ta+Rth(H)×{Pc(Q1)+Pc(Q4)}+Rth(j−c)1×Pc(Q1)

=50+54.4×(0.516+0.516)+3×0.516=107.7℃

と計算でき、

TjMAX=150℃に対しては71.8%になり目標値をクリアできます。

これらの値はヒートシンク単体での計算結果であり、半導体パッケージ表面からの放熱{130(K/W)}を考慮すれば温度上昇はもっと低くなりますのでこのまま設計を進めることにします。

なお、図10のように、熱の問題を熱抵抗回路網の問題に置き換えて解く手法は、回を改めて解説します。

次回はこのオーディオアンプを駆動する電圧増幅部についてモンテカルロ解析、ワーストケース解析を説明しながら設計を進めていきます。

執筆者プロフィール

加藤 博二(かとう ひろじ)

1951年生まれ。1972年に松下電器産業(現パナソニック)に入社し、電子部品の市場品質担当を経た後、電源装置の開発・設計業務を担当。1979年からSPICEを独力で習得し、後日その経験を生かして、SPICE、有限要素法、熱流体解析ツールなどの数値解析ツールを活用した電源装置の設計手法の開発・導入に従事した。現在は、CAEコンサルタントSifoenのプロジェクト代表として、NPO法人「CAE懇話会」の解析塾のSPICEコースを担当するとともに、Webサイト「Sifoen」において、在職中の経験を基に、電子部品の構造とその使用方法、SPICE用モデルのモデリング手法、電源装置の設計手法、熱設計入門、有限要素法のキーポイントなどを、“分かって設計する”シリーズとして公開している。

関連記事

SPICEモデルとライブラリ(その2)

SPICEモデルとライブラリ(その2)

必要なSPICEモデルがツールに含まれていない場合は、第三者提供のものを使う必要がある。第11回では、SPICEモデルの入手方法や、開発STEPとモデルの精度の考え方について説明する。有用なサブサーキットモデルについても紹介しよう。 SPICEモデルとライブラリ(その1)

SPICEモデルとライブラリ(その1)

設計した回路をSPICEで解析するには、使用している部品のSPICEモデルが必要だ。第10回では、このSPICEモデルについて解説する。

Copyright © ITmedia, Inc. All Rights Reserved.

【図10】等価熱抵抗回路網

【図10】等価熱抵抗回路網